#### **On-focal-plane ADC: Recent progress at JPL**

Zhimin Zhou, Bedabrata Pain, Roger Panicacci, Barmak Mansoorian, Junichi Nakamura<sup>+</sup>, and Eric R. Fossum

Center for Space Microelectronics Technology Jet Propulsion Laboratory - California Institute of Technology 4800 Oak Grove Drive, Pasadena, CA 91109

<sup>+</sup>Olympus America Inc., Torrance, CA 90505

#### ABSTRACT

Two 8 bit successive approximation analog-to-digital converters (ADC), an 8 bit single slope ADC, and a 12 bit current mode incremental sigma delta ( $\Sigma$ - $\Delta$ ) ADC have been designed, fabricated, and tested. The 20.4 µm and 40 µm pitch successive approximation test chip designs are compatible with active pixel sensor (APS) column parallel architectures. A 64 x 64 photogate APS with this ADC integrated on-chip was fabricated in a 1.2 µm N-well CMOS process and achieves 8 bit accuracy. A 1K x 1K APS with 11 µm pixels and a single slope ADC in each column was fabricated in a 0.55 µm N-well CMOS process and also achieves 8 bit accuracy. The successive approximation designs consume as little as 49 µW at a 500 KHz conversion rate meeting the low power requirements inherent in column parallel architectures. The current mode  $\Sigma$ - $\Delta$  ADC test chip is designed to be multiplexed among 8 columns in a semi-column parallel current mode APS architecture. It consumes 800 µW at a 5 KHz conversion rate.

## 1. INTRODUCTION

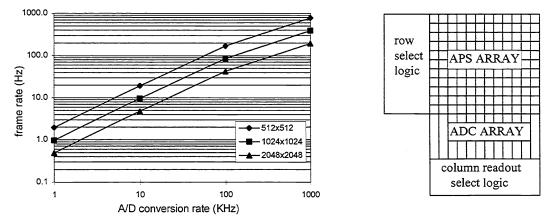

A key advantage to CMOS image sensors is the ability to integrate readout electronics on the same focal plane as the sensor as shown in figure 1. Through the use of standard CMOS technology there is available a wide variety of approaches to analog to digital conversion<sup>1,2,3,4,5,6,7</sup>. Sensor chip architectures placing analog to digital converters (ADC) in each column offer parallel conversion of an entire row of pixel data. This parallelism reduces the requirement for high speed ADCs (figure 1). For example, the minimum conversion speed of an ADC in each column of a 1024 x 1024 image sensor operating at a 30 Hz frame rate is approximately 33 KHz. Overhead for transferring off-chip the resultant digital image data can increase this speed requirement but can be overcome using either pipelined data transfer during the conversion or a high bandwidth digital output port.

Figure 1. Frame rate vs. ADC speed for a 512x512, 1024x1024, and 2048x2048 APS with the above column parallel architecture for focal plane A/D conversion (1.5 µsec row access time assumed).

A design tradeoff in placing an ADC per column is the low power requirement and increased physical size resulting from the small column pitch (10 to 40 µm depending on the process technology). A small pitch can also lead to column to column variations in ADC response because of poor device matching. To minimize these problems a compromise is possible, for

example, by multiplexing a single ADC per 8 columns.

Because both voltage mode and current mode active pixel sensors are used, there is a need for both voltage and current mode ADCs. The two successive approximation ADCs presented below operate in voltage mode and the sigma-delta ADC operates in a current mode. The successive approximation designs physically fit into a per column architecture and the sigma-delta fits onto an 8 column pitch where its operation is multiplexed.

The design and test results for each ADC are presented below. Section 2 reviews one of the first approaches used in column parallel ADC architectures<sup>3,7</sup> and presents a 1K x 1K image sensor using this ADC. Section 3 describes the operation and test results of a successive approximation ADC approach using switched capacitor op amp integrators. Section 4 presents a successive approximation ADC based on charge redistribution on a network of binary scaled capacitors. Also presented is a 64 x 64 CMOS APS with this ADC implemented on chip. Section 5 describes the operation and test results of the current mode sigma-delta ADC. Section 6 contains a summary of the four design characteristics.

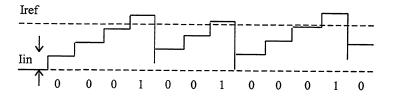

## 2. SINGLE SLOPE ADC

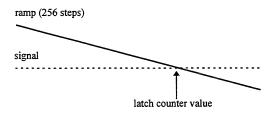

An advantage in using single slope ADCs in a column parallel architecture is the simplicity of its design. Each analog level in the ADC range is stepped through and compared to the input signal (figure 2). When the signal first exceeds this level, a count corresponding to the analog step is latched. For an 8 bit ADC 256 comparisons must be made. An on-chip

Figure 2. Single slope ADC ramp and signal levels during conversion

multiplying digital-to-analog converter (MDAC) is used to generate the ramp input. To increase its accuracy, the MDAC can be made relatively large compared to the ADC size because it can reside outside the column. Because of the large number of comparisons, this conversion method is slower than other methods.

## 2.1 Overview and test results of a 1K x 1K CMOS APS with on-chip single slope ADC

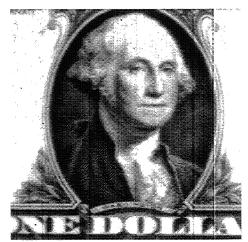

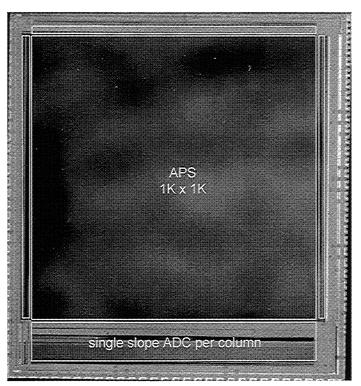

A 1K x 1K APS array with single slope ADCs per column and a ramp generator (MDAC) on-chip was fabricated in a 0.55  $\mu$ m CMOS N-well process with 11  $\mu$ m pixels. A 200 x 200 window image from the 8 bit digital readout port is shown in figure 3. A photograph of the 13.7 mm x 14.8 mm chip is shown in figure 4. The 1K x 1K APS array contains decoders for addressing rows and columns for window of interest readout of the array. Row decoders and row logic are placed on both sides of the array to speed up access to the array. In addition to the digital ADC readout mode, the sensor also contains an analog readout signal chain at the top of the array. The sensor with photo-diode pixels contains 3.6 million transistors and the sensor with photo-gate pixels contains 4.6 million transistors. The chip is powered from a 3.3V power supply.

Figure 3. Digital output from a 1K x 1K CMOS APS sensor with on-chip single slope ADC

Figure 4. Photograph of the fabricated 1K x 1K APS with onchip single slope ADC and ramp generator.

The per column 8 bit ADCs were characterized through a test port to the input of each ADC. Off chip counters are used as inputs to the ADC latches and MDAC circuit. For ADC characterization the 8 bit digital output of the ADC was passed through an off chip 8 bit DAC for convenient display on an oscilloscope and capture by the host computer test system. The test system also generates the signal input to the ADC through the test port.

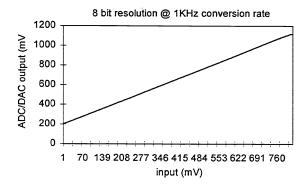

For slow conversion speeds (1KHz) the single slope ADC is accurate to 8 bits. The transfer curve of the ADC is shown in figure 5. At higher speeds the ramp introduces errors into the conversion. At a 12.5 KHz conversion rate, the ADC has 6 bits of accuracy. Additional characteristics are listed in table 2. For these tests the ADC-DAC output range is 0.9V, the ADC reference is 0.4V, and the gain of the input stage to the ADC is 0.5.

Figure 5. Transfer curve for one of the column parallel single slope ADCs

#### 3. SWITCHED-CAPACITOR SUCCESSIVE APPROXIMATION ADC

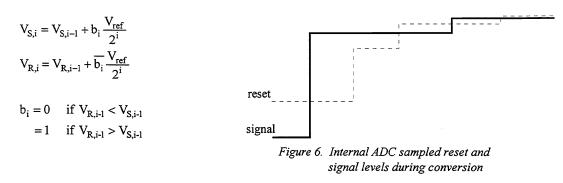

The successive approximation approach to analog-to-digital conversion is essentially a "ranging" algorithm. The new feature in the successive approximation ADCs presented below is the double sided approach to conversion. The ADC attempts to add successive binary fractions of a reference voltage to either the pixel signal or reset level until they are equal. In this way if a comparison result is false, the ADC saves a step by not having to remove the previously added reference fraction from the signal. The ADC was designed for an APS sensor with a readout scheme where the pixel reset voltage is greater than the pixel signal level as in [8]. The voltage levels at each step "i" in the conversion are shown in figure 6 and are described by:

#### 3.1 Design and operation

The first design approach uses two switched-capacitor integrators to perform the successive approximation analog to digital conversion. This successive approximation method attempts to find the digital representation of the pixel signal relative to the pixel reset level. It does this conversion by successively adding binary scaled fractions of a reference voltage to either the readout pixel signal voltage or pixel reset voltage until the two values are equal to within the desired accuracy or one least significant bit (LSB).

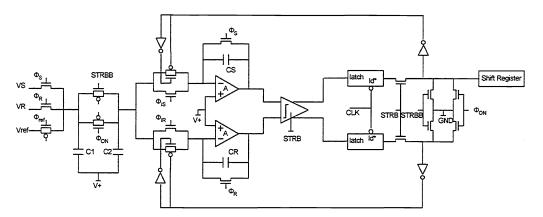

The schematic of the ADC is shown in figure 7. The ADC has two inputs for pixel signal and reset levels (VS and VR). There is also an input for the ADC voltage reference range. All input voltages are referenced to V+. The top op amp integrator stores the pixel signal level and the bottom op amp integrator stores the reset level. Both integrators are inputs to a comparator. During the  $\Phi_{ON}$  interval the pixel signal level, reset level, and ADC reference are sampled onto the 2.5 pF capacitors C1 and C2. The top and bottom integrators are reset to V+ during  $\Phi_S$  and  $\Phi_R$ , respectively. The signal level, VS-V+, is sent to the top integrator input during the  $\Phi_S/\Phi_{IS}$  interval. With a 5 pF op amp feedback capacitor, the integrator gain is -1. Thus, the value V+ - VS is added to integrator output voltage. The reset level, V+-VR, is similarly added to the bottom integrator output during the  $\Phi_R/\Phi_{IR}$  interval. The reference level (Vref-V+) is stored on C1 and C2 during  $\Phi_{REF}$ .

After the inputs are read into the ADC,  $\Phi_{ON}$  turns off and the first comparison is performed to determine the sign bit (typically 0 for the image sensor). The comparator is activated when the STRB\* signal goes low. Otherwise both comparator outputs are 0. If the signal side is greater than the reset side, the comparator output into the shift register is a 0. In this case, the feedback from the comparator output sets the switches on the front end to steer the reference on C2 to the integrator on the reset side holding the lower output voltage. Because C1 is cutoff from C2 during this time, the gain of the integrator is -0.5 (= 2.5pF/5pF). Thus, (V+-Vref)/2 is added to the integrator output. For correct operation V+ > Vref so that the voltage is increased on integrator with the lower output voltage.

During the second comparison, the MSB is determined and stored in the shift register. Before this comparison is performed, the feedback path from the comparator is shut off disconnecting the inputs to the integrator. During the comparison half the charge on C1 is transferred to C2. The resulting voltage across on C2 is (Vref-V+)/2. Subsequently, C1 is cutoff from C2, the comparison is made, and (V+-Vref)/4 is transferred to the output of the integrator with the lower output voltage (reset side if the original pixel signal is more than 1 MSB larger than the reset level, otherwise to the signal side).

Figure 7. Successive approximation ADC circuit using switched capacitor integrators

The binary scaled fraction of the reference voltage is always added to the integrator with the lower voltage stored on it. The integration and comparison steps are performed until the desired number of bits is achieved. A shift register per column stores the comparator output for readout of the digital word at the end of the conversion.

One of the key components in this design is the switched capacitor integrator. To achieve at least 8 bit resolution, an op amp with a gain of 60 dB (1,000) is required<sup>1</sup>. The op amp used in this design is a single stage folded cascode op amp.

## 3.2 Test results

The ADC was characterized using a 1V ramp to drive the input from a computer controlled data generator/acquisition board.

Figure 8. Transfer curve for a successive approximation ADC implemented with switched capacitor circuits.

The analog input was incremented in 1mV steps and 500 ADC output samples at each step were acquired. ADC output was passed through a digital-to-analog converter (DAC). The analog output of the ADC/DAC was connected to the computer acquisition board where it was measured. The DAC has an offset voltage of 0V and a -1V reference.

The ADC was characterized at different speeds and power levels. Because of the application of this ADC to the column parallel architecture of a CMOS image sensor, the maximum power dissipation desirable from the ADC is approximately 150 to 200  $\mu$ W. At these power levels, the ADCs in a 1K x 1K image sensor consume 150 to 200 mW.

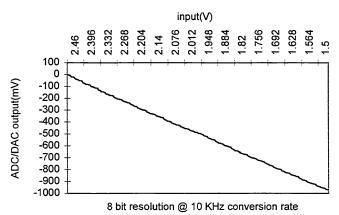

For a power dissipation of 175  $\mu$ W and 8 bit resolution, the maximum conversion rate is 50 KHz or 20  $\mu$ seconds/conversion. The maximum 1K x 1K sensor frame rate for this conversion speed is approximately 45 Hz. Integral non-linearity (INL), differential non-linearity (DNL), and ADC noise were measured (Table 2). The ADC noise is determined from the worst case standard deviation calculated from the 500 samples taken at each input step. Based on the non-linearites, the effective ADC accuracy is 5 bits. The ADC operating at a 10 KHz conversion rate worked at a minimum power of 27  $\mu$ W. Its effective accuracy is also 5 bits. The transfer curve for the ADC operating under best case conditions at 10 KHz and 134  $\mu$ W power level is shown in figure 8.

Stand alone op amps on the test chip were characterized at various power levels. The op amp had a gain of 74 dB and consumed 70  $\mu$ W. At a low power dissipation level of 20  $\mu$ W, the op amp had a gain of 80 dB. However, at the low bias current levels, the op amp slew rate limited the ADC speed.

## 4. BINARY SCALED CAPACITOR SUCCESSIVE APPROXIMATION ADC

This approach to ADC design uses a dual networks of binary scaled capacitors to sample pixel signal and reset voltages. These capacitor networks are connected to the input of a comparator. After clamping these levels on the top plate of the capacitors, the bottom plates are successively connected to the ADC reference voltage. The voltage increase on the top plate is proportional to the relative size of the capacitor to the total capacitance of the network. The comparator output determines which side sees an increase in the top voltage similarly to the switched capacitor integrator approach. This method of using binary scaled capacitors to perform analog to digital conversion is similar to [9]. This ADC uses the same new feature as the switched capacitor design presented in the previous section where a double sided approach is used to increase converter speed.

# 4.1 Design and operation

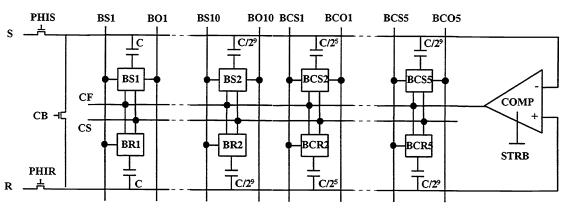

Figure 9. Binary scaled capacitor successive approximation ADC

The block diagram of the dual sided binary scaled capacitor successive approximation ADC is shown in figure 9. Each of the latches (BS#9-BR#0) contains a switch either to ground or to the ADC voltage reference as shown in figure 10. If the enable to the latch BS#n on the signal side is active and the comparator output is high (reset input > signal input at the comparator), the bottom plate of the capacitor is switched from 0 to Vreference. If the same enable to the latch BR#n on the reset side is active and the comparator output is high (reset input > signal input at the reset side is active and the comparator output is low (signal input > reset input at the comparator), the bottom plate of the

capacitor is switched from 0 to Vreference. The latch connected to the largest capacitor C contains the sign bit. When the sign bit is 1, the voltage on the signal side increases by Vref x (C/Ctotal) where:

$$C_{TOTAL} = C + C/2 + C/4 + C/8 + C/16 + C/32 + C/64 + C/128 + C/256 + C/512 = 1.998C.$$

Thus, the operation is similar to the integrator approach where Vref/2 is added to the signal side after the first comparison if the signal is greater than the reset level. The value of the largest capacitor used is 4 pF.

The latches on the signal side contain the final binary word at the end of the conversion. Because the charge redistribution on the top plates is relatively fast compared to the charge transfer in the switched capacitor integrator approach, the ADC conversion rate is higher. Also, it consumes less power and is less sensitive to process non-uniformities because no op amps are required. However, placing a total of 16 pF of capacitance per column consumes a large amount of silicon area.

Also included in the ADC are 5 capacitor bit cells for storing the comparator offset. This offset is calculated at the end of each conversion by enabling the CB switch. When this switch is enabled both inputs to the comparator are set equal so that the offset can be measured and stored for off chip correction.

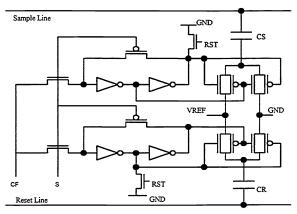

Figure 10. Bit cell latch/switch to the capacitor bottom plates for the signal and reset sides

## 4.2 ADC Test results

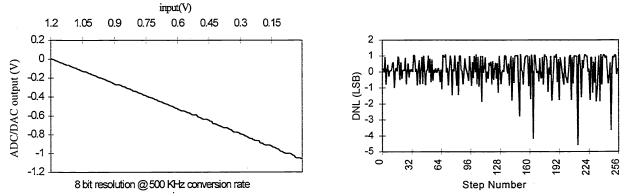

The ADC was characterized in a similar manner as the op amp integrator successive approximation ADC. A 1.2V input ramp with 256 steps was used to drive the ADC input. Noise measurements were based on 200 samples at each step.

Figure 11. Transfer curve and DNL error at 500 KHz conversion rate for the successive approximation ADC implemented with a binary scaled capacitor network.

The transfer curve and the differential non-linearity plot of the ADC at a 500 KHz conversion rate are shown in figure 11. The effective accuracy of the ADC at a 500 KHz rate is 5 bits (Table 2). The ADC operated as high as 833 KHz with the same accuracy except for 4 input levels that generated large DNL and INL errors. The ADC consumed 49  $\mu$ W at the 500 KHz speed. The power dissipation is primarily from the comparator and CV<sup>2</sup>f component in charging the capacitor network.

The maximum frame rate for a  $1K \times 1K$  sensor using this 500KHz ADC conversion rate is 279 Hz. The frame rate will be less depending on the bandwidth and timing of the sensor's digital output port.

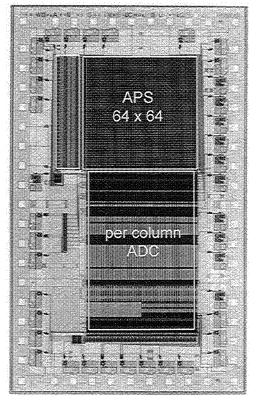

## 4.3 Test results from a CMOS APS imager with on-chip ADC

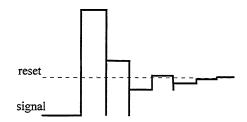

A variation in the ADC design using only a single bank of capacitors on the signal side was integrated with a  $64 \times 64$  CMOS active pixel image sensor. The operation of the adc is similar to the double sided capacitor approach but operates only on the signal level during conversion (figure 12).

Figure 12. Timing of internal ADC sampled reset and signal levels during conversion for a single bank of capacitors on the signal side.

This design was fabricated in a 1.2  $\mu$ m N-well CMOS process with linear capacitors. The 8 bit ADC size is 24  $\mu$ m x 2.2 mm. The photogate pixel is 24  $\mu$ m x 24  $\mu$ m. An 8 bit image from a 64 x 32 window from the sensor is shown in figure 13. A decoder is used to address rows and columns in the array to generate the window of interest readout. A photograph of the 3.0 mm x 5.0 mm chip is shown in figure 14.

The ADC integrated on-chip was operated without using the offset correction bits. In this mode the ADC has less than 2 LSBs of fixed pattern noise across the 64 column parallel ADC array. This corresponds to a maximum of 7 mV of variation in the comparator input offset voltage from column to column.

The ADCs were characterized through a test port connected directly into the ADC input. At a 70 KHz conversion rate, the measured INL was 1 LSB and the DNL was 0.8 LSB.

Although the single sided capacitor network approach is slower than the double sided approach, it requires much less area. The accuracy is also better because the capacitor matching requirement between the two banks is eliminated.

Figure 13. 64 x 32 APS image with onchip successive approximation ADC.

Figure 14. Photograph of fabricated 64 x 64 active pixel sensor with on-chip successive approximation ADC.

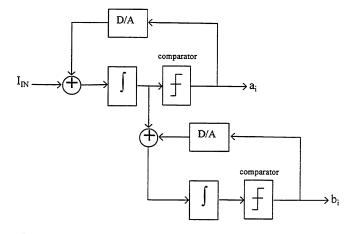

# 5. CURRENT MODE SECOND ORDER INCREMENTAL SIGMA DELTA ADC

Oversampling methods for ADC design are attractive because they avoid many of the difficulties with conventional methods for A/D and D/A conversion. Conventional converters require high precision analog circuits. On the other hand oversampling converters, can use simple and relatively low precision analog components. Unlike the voltage mode approach for sigma delta modulation in [2], this current-mode approach uses no MOS op-amps or linear capacitors. The main building block is a current copier cell. Though they require fast and complex digital signal processing stages, their robustness is suited for fast growing VLSI technology.

Figure 15. Typical  $\Sigma$ - $\Delta$  event sequence

A first-order  $\Sigma$ - $\Delta$  ADC requires 2<sup>n</sup> cycles to perform a n-bit A/D conversion. The accumulator and comparator output levels are shown in figure 15. Typically the comparator output is used to increment a counter that at the end of the conversion contains the digital number representation of the analog input. Conversion speed can be significantly increased by cascading two first order stages, resulting in an incremental  $\Sigma$ - $\Delta$  ADC topology. The architecture of the current-mode second-order incremental  $\Sigma$ - $\Delta$  modulator is based on the one reported in [10].

## 5.1 Design Overview

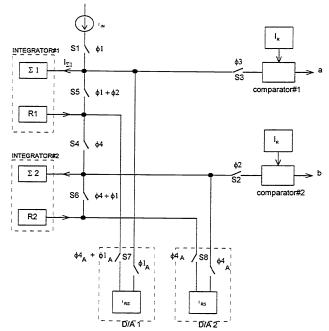

Figure 16 shows a block diagram of the current-mode second-order incremental  $\Sigma$ - $\Delta$  modulator. The three main building blocks are the current integrator, current comparator, and the digital to analog current converter. There are two loops, connected in cascade. Output of the comparator, "a" for the first comparator and "b" for the second one, becomes "1" if the output of the integrator, I, is greater than the reference current I<sub>REF</sub>. Otherwise it is "0". A D/A converter in the feedback loop outputs -I<sub>REF</sub> if the output of the comparator is "1", otherwise it outputs no current.

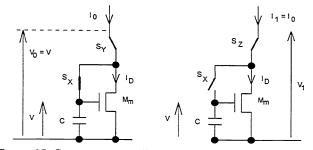

The basic building block of these components is the current copier cell. The principle of a current copier cell, also called a dynamic current mirror, is shown in figure 17. A single transistor  $M_m$  is combined with 3 switches  $S_X$ ,  $S_Y$ , and  $S_Z$  that are implemented by means of additional transistors, and a capacitor C. In the first phase (phase 0),  $M_m$  operates as the input device of a mirror, with its gate and drain connected to the input current source. When equilibrium is reached, capacitor C at the gate is charged to the gate voltage V required to obtain  $I_D = I_0$ . The value of  $I_0$  is thus stored as a voltage across C. In the second phase (phase 1), M<sub>m</sub> operates as the output device of a mirror, with its drain disconnected from the gate and connected to the output node. It sinks an output current I1, that is

Figure 16. Block diagram of the second order sigma-delta ADC

Figure 17. Current copier cell in memorize mode (left) and output mode(right).

controlled by the same gate voltage V and thus is equal to  $I_0$ .

#### **5.2 Operation**

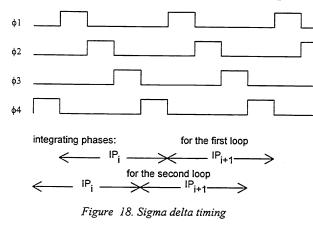

The detailed operation of the converter based on the block diagram in figure 19 is as follows: Each integration period consists of 4 phases (figure 18). Phase 1 is used to sample the input current. For the first integration period "i", the register in the first integrator is zero. Thus, during phase 1 only the input current is memorized at integrator#1's

summing current copier. During phase 2, the output of the summer is copied to integrator#1's register. Phase 3 is used to compare the summing current copier to the reference current. If this copier cell current is greater than the reference,  $a_1$  is a "1". In phase 4 the output of the integrator#1's register is memorized by integrator#2's summing current copier. If  $a_1$  is a "1" the reference current is subtracted from the output of the first integrator's register. During the beginning of integration period "i+1" starting with phase 1, integrator#1 memorizes the sum of the output of its register and the input current. If  $a_1$  is a "1" the reference current is also subtracted from this sum.

The timing for the second integrator is the same as the first integrator except the above operations are offset by one phase. During phase 1 (following the phase 4 cycle during which integrator#1's register output was memorized) the current from integrator#2's summing current copier is copied to integrator#2's register. During phase 2, the comparison takes place between the summing current copier and the reference current. No events occur during phase 3. During the beginning of the next integration period for the second integrator starting with phase 4, the summing copier memorizes the sum of the output of its register and the output of integrator#1's register. In addition, the reference current is subtracted if the output of the comparison during phase 2 resulted in  $b_i$  equal to "1".

The expressions for two integrator's summing current copier cells at the end of "p" integration cycles are:

$$I_{\Sigma1}[p,3] = p \cdot I_{in} - \sum_{i=1}^{p-1} a_i \cdot I_{ref}$$

$$I_{\Sigma2}[p,2] = \frac{(p-1) \cdot p}{2} \cdot I_{in} - \sum_{i=1}^{p-1} a_i \cdot (p-i) \cdot I_{ref} - \sum_{i=1}^{p-1} b_i \cdot I_{ref}$$

At the end of p integration cycles the digital representation of the sigma delta output is determined by:

$$DN = \sum_{i=1}^{p-1} a_i \cdot (p-i) + \sum_{i=2}^{p-1} b_i$$

The digital filter consisting of a counter and accumulator is used to generate the digital number. The relationship between resolution of the ADC and number of integration cycles p (number of times the input current is sampled) is shown in table 1. The digital filter for the test chip was implemented off-chip.

#### 5.3 Test results

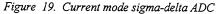

The ADC was tested using a computer controlled current source and the output data from the off-chip digital filter was read by the computer data acquisition board. The input current ramp consisted of 4096 steps of 4nA each. At each input step 20 samples were acquired. The DC current bias was 40  $\mu$ A. The transfer curve is shown in figure 20.

The 12 bit ADC consumed a total of 800  $\mu W$  when operating at a 5 KHz conversion rate. From differential non-linearity measurements the accuracy of the ADC is 10 bits.

| resolution<br>n (bits) | p<br>(oversampling<br>ratio) |  |  |  |  |

|------------------------|------------------------------|--|--|--|--|

| 6                      | 12                           |  |  |  |  |

| 7                      | 17                           |  |  |  |  |

| 8                      | 24 33                        |  |  |  |  |

| 9                      |                              |  |  |  |  |

| 10                     | 46                           |  |  |  |  |

| 11                     | 65                           |  |  |  |  |

| 12                     | 92                           |  |  |  |  |

| 13                     | 129                          |  |  |  |  |

| 14                     | 182                          |  |  |  |  |

Table 1. Relationship between ADC resolution and integration cycles "p".

Figure 20. Transfer curve and DNL error at 5 KHz conversion rate for 12 bit incremental sigma delta ADC.

#### 6. SUMMARY

Column parallel architectures of CMOS active pixel sensors require low power compact analog-to-digital converters. Two types of successive approximation ADC designs and a current mode sigma delta ADC design for integration into CMOS active pixel sensors were demonstrated. A 1K x 1K CMOS APS with a single slope ADC and a 64 x 64 CMOS APS with a successive approximation ADC per column of the array were also demonstrated. Table 2 lists their characteristics. For voltage mode APS sensors, the 8 bit successive approximation ADC using binary scaled capacitors achieves the highest speed and accuracy. This ADC's new feature of using dual capacitor banks to achieve high speed enables the development of high frame rate sensors. The current mode sigma delta converter has the highest accuracy of the ADC designs. Its inherent robustness makes it ideal for application in high accuracy CMOS image sensors.

|                                              | Res    | Accurac          | y . |       | Conv. | Power   | Power/     | CMOS    | Size                 |

|----------------------------------------------|--------|------------------|-----|-------|-------|---------|------------|---------|----------------------|

|                                              | (Bits) | (LSBs)           |     |       | rate  | dissip. | Conv. rate | process |                      |

| ADC TYPE                                     |        | DNL <sup>+</sup> | INL | NOISE | KHz   | μW      | µW/kHz     | (µm)    |                      |

| single slope                                 | 8      | 0                | 0.8 | 0.65  | 1     | 24      | 24.0       | 0.55    | 11 μm x 1.43 mm      |

|                                              | 8      | 2                | 5   | 3.8   | 12.5  | 34      | 2.7        |         |                      |

| op-amp S.A.                                  | 8      | 3                | 6.5 | 2     | 50    | 175     | 3.5        | 1.2     | 20.4 µm x 1.94 mm    |

|                                              | 8      | 3                | 5.9 | 2.9   | 10    | 134     | 13.4       |         | (without shift reg.) |

|                                              | 8      | 2                | 5   | 2.25  | 10    | 27      | 2.7        |         |                      |

| double sided scaled                          | 8      | 5                | 3.5 | 8     | 500   | 49      | 0.1        | 2.0     | 40 µm x 4.2 mm       |

| capacitor S.A.                               | 8      | 4*               | 5*  | 21*   | 833   | 55      | 0.07       |         |                      |

| single sided S.A.                            | 8      | 0.8              | 1   |       | 70    |         |            | 1.2     | 24 µm x 2.2 mm       |

| current mode incremental $\Sigma$ - $\Delta$ | 12     | 2                | 10  | 2.5   | 5     | 800     | 160.0      | 2.0     | 80 µm x 1.92 mm      |

\* removing selected non-linear data points

<sup>+</sup> units are +/-

Table 2. Summary of ADC designs and test results.

#### 7. ACKNOWLEDGMENTS

The research described in this paper was performed by the Center for Space Microelectronics Technology, Jet Propulsion Laboratory, California Institute of Technology, and was sponsored in part by the Defense Advanced Research Projects Agency Electronic Systems Technology Office (DARPA/ESTO) Low Power Electronics Program, and the National Aeronautics and Space Administration (NASA). JN is supported by Olympus America, Inc.

## 8. REFERENCES

<sup>1</sup> B. Pain, E.R. Fossum, "Approaches and analysis for on-focal-plane analog-to-digital conversion," in <u>Infrared Readout</u> <u>Electronics II</u>, Proc. SPIE, vol. 2226, pp. 208-218 (1994).

<sup>2</sup>S.K. Mendis, B. Pain, R.H. Nixon, and E.R. Fossum, "Design of a low-light-level image sensor with on-chip sigma-delta analog-to-digital conversion", in <u>CCD's and Optical Sensors III</u>, Proc. SPIE vol. 1900, pp. 31-39 (1993)

<sup>3</sup> A. Dickinson, S. Mendis, D. Inglis, K. Azadet, and E. Fossum, "CMOS digital camera with column parallel analog-todigital conversion architecture," 1995 IEEE Workshop on CCDs and Advanced Image Sensors, Dana Point, CA, April 20-22 1995.

<sup>4</sup> B. Fowler, A. Gamal, and D. Yang, "A CMOS area image sensor with pixel-level A/D conversion," IEEE ISSCC Tech. Dig. pp. 226-227 (1994).

<sup>5</sup> K. Chen, M. Afghahi, P. Danielsson, and C. Svensson, "PASIC - A Processor-A/D converter sensor integrated circuit," IEEE ISCAS, pp. 1705-1708 (1990).

<sup>6</sup> R. Forchheimer, P. Ingelhag, and C. Jansson, "MAPP2200: a second generation smart optical sensor," Proc. of SPIE vol. 1659 <u>Image Processing and Interchange</u>, pp. 2-11 (1992).

<sup>7</sup> C. Jansson, O. Ingelhag, C. Svensson, and R. Forchheimer, "An addressable 256x256 photodiode image sensor array with an 8-bit digital output," Analog Integrated Circuits and Signal Processing, vol. 4, pp. 37-49 (1993).

<sup>8</sup>R.H. Nixon, S.E. Kemeny, C.O. Staller, and E.R. Fossum, "128 x 128 CMOS photodiode-type active pixel sensor with onchip timing, control and signal chain electronics," in <u>Charge-Coupled Devices and Solid-State Optical Sensors V</u>, Proc. SPIE vol. 2415, paper 34 (1995).

<sup>9</sup> J.L. McCreary, P.R. Gray, "All-MOS Charge Redistribution Analog-to-Digital Conversion Techniques-Part I," in IEEE J. Solid State Circuits, vol. SC-10, pp. 371-379, Dec. 1975.

<sup>10</sup> J. Robert and P. Deval, "A second-order high resolution incremental A/D converter with offset and charge injection compensation," in IEEE J. Solid State Circuits, vol. 23, pp. 736-741, June 1988.